Handel-CとEDIFの相互利用

Celoxica社のHandel-Cの中でEDIFモジュールをブラックボックスとして取り込んだり、また逆にHandel-Cで書いたモジュールをEDIFに変換する際に、他の言語や回路ツールでブラックボックスとして取り込めるようにするための方法です。これとViewDraw (ePD DxDesinger) とHDLの相互利用方法により、EDIFを介してViewDraw, HDL, Handel-Cの全てで相互利用(モジュール化とそのインターフェース)が可能です。

解説内容は以下の2つです。

- EDIFモジュールをHandel-C中で使う方法

- Handel-Cモジュールを他で取り込めるEDIFモジュールにする方法(まだ)

各ツールのバージョン

| 製品名 | バージョン |

|---|

| Handel-C 開発環境 | DK | Ver.2.0 with SP2 |

| Handel-C Compiler | Ver.3.2.2710(標準のDK2だと2701) |

| インプリメンテーションツール | XILINX ISE Foundation | 5.2.03i |

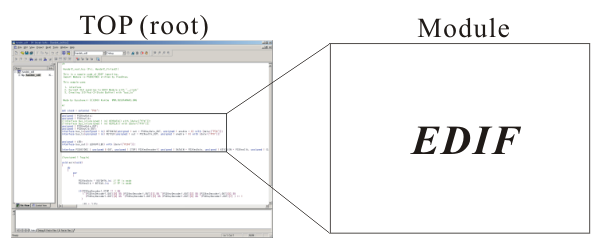

1. EDIFモジュールをHandel-C中で使う方法

Handel-CとEDIFとのインターフェースには基本的に"interface"文を用います。

EDIFモジュールを取り込む場合は、この"interface"を使ってEDIF中で定義されている

ピン名とHandel-Cの中で使いたい名前を対応付けるだけです。ポイントはクロックの供給

方法でしょうか・・

手順:

- DKにて

- EDIFモジュールを呼び出す側のHandel-Cのソースを作る

- interfaceの構文は、「interface EDIFモジュール名(EDIFモジュールからの出力ピン名) Handel-C中で扱うモジュールの名前(EDIFモジュールへの入力ピン名 = Handel-C中で扱う変数名);」である。入出力ピンが複数ある場合はそれぞれ","(カンマ)で区切って並べる

- EDIFモジュールを呼び出すHandel-Cの中で使っているクロック(set clock = external "XX"; など)を、そのままEDIFモジュールのCLK入力ピンに供給したい場合は、"interface"構文中で「unsigned 1 CLK = __clock」などとする。ここで"__clock"がカレントのクロックを指しており、例ではこれをEDIFモジュールの"CLK"という入力ピンと接続している

- ISEにて

- ISEにて、「ファイル」->「新規プロジェクト」でプロジェクトを作成。ここで、"Design Flow"を「EDIF」にすること

- 「プロジェクト」->「ソースの追加」で、対象となる「EDIFモジュールを用いた最上位のHandel-Cから生成したEDIFファイル」を追加

- "Implement Design" のプロパティ中の "Translate Properties" にある "Macro Search Path" に、埋め込むEDIFモジュールのファイルのあるディレクトリを指定する

- インプリメンテーションを実行して完成

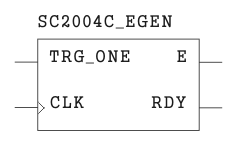

例: ここではSUSUBOXの一つで、キャラクタLCDドライバの一部の簡単なモジュールである"SC2004C_EGEN"(ViewDrawで記述されている)のEDIFファイル(sc2004c_egen_35p71m.edn)

を"handelc_root.hcc"から呼び出してみます。

"sc2004c_egen_35p71m.edn"は28.58MHz以上〜35.71MHz未満のベースクロックで規定時間のパルスを生成するモジュールですが、この範囲外の周波数でも動作はするので、EDIFの呼び出しテストには問題ありません。

呼び出すEDIFモジュール

Handel-Cのサンプル・ソースファイル:handelc_root.hcc

※ピン・アサイン("Pxx")は任意に置き換えてください。

set clock = external "P92"; // CLK Pin Assign

unsigned 1 x = 0; // Internal Variable for "TRG_ONE"

interface bus_in(unsigned 1 an_Input) TRG_ONE_IN() with {data={"P209"}}; // Input Pin Assign

unsigned 1 y; // Internal Variable for "E"

unsigned 1 z; // Internal Variable for "RDY"

interface bus_out() E_OUT(unsigned 1 out = y) with {data={"P217"}}; // Output Pin Assign

interface bus_out() RDY_OUT(unsigned 1 out = z) with {data={"P216"}}; // Output Pin Assign

interface sc2004c_egen_35p71m(unsigned 1 E, unsigned 1 RDY) EpulseGenerator1(unsigned 1 TRG_ONE = x, unsigned 1 CLK = __clock); // EDIF Import

unsigned 1 SingleREG = 0;

void main(void)

{

do

{

par

{

/* Single Shot Pulse Making */

if(TRG_ONE_IN.an_Input == 1)

{

if(SingleREG == 0)

{

x = 1; // The sc2004c_egen_35p71m's TRG_ONE is set 1.

x = 0; // The sc2004c_egen_35p71m's TRG_ONE is set 0.

SingleREG = 1;

}

}

else

{

SingleREG = 0;

}

/* EDIF module outputs assign */

y = EpulseGenerator1.E; // sc2004c_egen_35p71m's E outputs to the y.

z = EpulseGenerator1.RDY; // sc2004c_egen_35p71m's RDY outputs to the z.

}

}

while(1);

}

|

一応Virtex-E(XCV300E-6PQ240C)にて動作確認済みですが、Handel-Cはまだほとんど使ったことがないので、基本的な間違いとかがあったらご指摘ください。^^;(コメントの英語がまちがってるとか・・)

シングル・ショット・パルスなどはこんな記述でいいのでしょうか・・??

あ、外部からシングル・ショット・パルスを入力することを前提に、もっと単純に書くとmain()文内は下記のようになります。

void main(void)

{

do

{

par

{

x = TRG_ONE_IN.an_Input; // The TRG_ONE_IN outputs to sc2004c_egen_35p71m's TRG_ONE.

/* EDIF module outputs assign */

y = EpulseGenerator1.E; // sc2004c_egen_35p71m's E outputs to the y.

z = EpulseGenerator1.RDY; // sc2004c_egen_35p71m's RDY outputs to the z.

}

}

while(1);

}

|

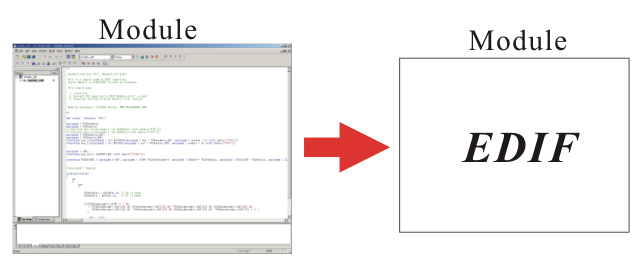

2. Handel-Cモジュールを他で取り込めるEDIFモジュールにする方法(まだ)

こっちは基本的に"interface port"文でできるようです。問題はやはりベースクロックの外部入力方法(CLKピンの作り方)でしょう。

ヒント?

interface port_in (unsigned 1 CLK_IN) ClkInputPort(); // Making a CLK Input Port named "CLK_IN".

set clock = internal ClkInputPort.CLK_IN; // Using External Clock from ClkInputPort.

interface port_in(unsigned 1 TRG_ONE) XXX(); // Making an Input Port named "TRG_ONE".

interface port_out() YYY(unsigned 7 DataOut = DOUT); // Making a Output Port named "DOUT".

|

最初の行の"CLK_IN"のあとに"with {clockport = 1}"を入れるとか入れないとか・・?

未検証です。まちがってたらごめんなさい。^^;;

by すすたわり (2004.01.06)

(2004.01.16 更新)

ご意見、ご感想などはこちらまで。

E-mail: susu@susutawari.org

Copyright (C)2003-2004 N.Aibe. All Rights Reserved.